Si vous souhaitez lancer une dispute lors d’une réunion Hackaday, il vous suffit de demander quelque chose comme « Combien cela pèse-t-il ? ou « Quelle heure est-il? » Mais si vous voulez vraiment déclencher une bagarre de rue, vous pouvez toujours dire : « Ces chiffres sont-ils aléatoires ? Créer des nombres aléatoires qui sont réellement aléatoires est en fait un problème difficile à résoudre. Techniquement, la plupart de ce que nous faisons est pseudo-aléatoire (mais nous dirons un nombre aléatoire et supposerons que vous comprenez ce que nous voulons dire). Une façon de générer des séquences apparemment aléatoires consiste à utiliser un registre à décalage à rétroaction linéaire ou LFSR. Vous pouvez utiliser les LFSR dans des logiciels, mais ils sont également très utiles dans la conception matérielle et [Adam Taylor] nous présente son utilisation sur les FPGA dans un article récent.

Comme [Adam] souligne qu'ils génèrent non seulement des modèles aléatoires, mais qu'ils sont souvent utilisés comme compteurs hautes performances et dans des systèmes de détection et de correction d'erreurs. Comme son nom l'indique, le mécanisme est un simple registre à décalage dont une ou plusieurs de ses sorties sont renvoyées vers l'entrée. Comment cela peut-il être aléatoire ? Eh bien, ce n'est pas possible, mais c'est souvent suffisant pour les endroits où vous avez besoin d'une séquence de nombres. Selon la façon dont vous organisez les sorties – ou les prises – et la façon dont vous les renvoiez, vous pouvez contrôler la séquence pseudo-aléatoire.

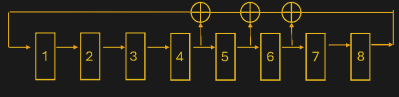

Il existe deux méthodes courantes pour créer des LFSR. Une conception de style Fibonacci utilise des portes XOR (ou XOR inversé) dans la boucle de rétroaction. Par exemple, considérons un compteur à huit étages. Le message montre la sortie de la bascule 4, alimentant une porte XOR qui pilote l'entrée du compteur. L'autre entrée de la porte XOR est la sortie d'une autre porte XOR qui reçoit l'entrée de la bascule 5 et la sortie d'encore une autre porte XOR. Cette porte XOR reçoit ses entrées de la bascule 6 et la sortie du registre à décalage.

Le schéma de Galois est similaire, mais utilise les portes XOR dans le chemin de décalage. En d’autres termes, la sortie du registre à décalage alimente directement l’entrée, mais elle alimente également plusieurs portes XOR qui passent entre les bascules. Pourquoi choisir l’un plutôt que l’autre ? Lisez le message. Le résumé est que cela dépend de la façon dont votre FPGA se réinitialise et du type de prise en charge dont il dispose pour les registres à décalage. Ainsi, comme d'habitude, il est utile de comprendre ce qui se passe dans la structure FPGA.

Quant à l’endroit où placer les robinets, cela dépend de la manière dont vous souhaitez que le motif se répète. Si vous souhaitez que les répétitions soient réduites au minimum, vous pouvez les rechercher dans un tableau basé sur des recherches menées par [Wayne Stahnke] et popularisé par Xilinx dans une note d'application. [Solomon Golumb] a également publié des tableaux de taps pour une génération de séquence maximale. Comme vous vous en doutez, il existe un programme qui vous aidera si vous ne souhaitez pas utiliser les tables.

Le calcul est peut-être délicat, mais sa mise en œuvre matérielle est simple si jamais vous avez besoin d'une séquence d'apparence aléatoire. Peut-être que vous voulez un scintillement aléatoire dans votre fausse bougie. Vous pouvez même le faire avec des relais.