Nous avons commencé la semaine dernière à concevoir une carte PCIe, un adaptateur de clé électronique M.2 à clé électronique, qui ajoute un lien supplémentaire à l’emplacement pour clé électronique qu’il contient – utile pour utiliser pleinement quelques cartes de clé électronique rares mais sophistiquées. À présent, le schéma est terminé, le placement des composants a été déterminé et nous n’avons qu’à router les paires différentielles – cela devrait être simple, non ? Bouclez votre ceinture.

Faire les Diffpairs

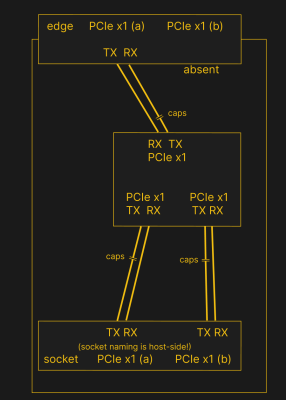

PCIe a besoin de paires TX connectées à RX à une autre extrémité, comme UART – et cela n’est pas négociable. Les connecteurs utiliseront la dénomination côté hôte et vice-versa. Comme le montre le schéma, nous connectons le TX du socket au RX de la puce et vice-versa ; si jamais nous sommes confus, le schéma de l’ordinateur portable est là pour nous aider à clarifier les choses. Pour résumer, il suffit d’inverser les noms sur le lien venant au commutateur PCIe, puisque le commutateur PCIe agit comme un périphérique sur la carte ; les deux liaisons du commutateur vont à la prise E-key et, pour les besoins de cette prise, le commutateur PCIe agit comme un hôte.

PCIe a besoin de paires TX connectées à RX à une autre extrémité, comme UART – et cela n’est pas négociable. Les connecteurs utiliseront la dénomination côté hôte et vice-versa. Comme le montre le schéma, nous connectons le TX du socket au RX de la puce et vice-versa ; si jamais nous sommes confus, le schéma de l’ordinateur portable est là pour nous aider à clarifier les choses. Pour résumer, il suffit d’inverser les noms sur le lien venant au commutateur PCIe, puisque le commutateur PCIe agit comme un périphérique sur la carte ; les deux liaisons du commutateur vont à la prise E-key et, pour les besoins de cette prise, le commutateur PCIe agit comme un hôte.

Lors du routage initial de cette carte, j’ai absolument oublié une chose importante pour les condensateurs série PCIe sur chaque paire de données, du côté hôte TX de la liaison. Nous avons besoin de trois paires de condensateurs ici – sur TX de la liaison montante du commutateur PCIe et deux paires sur le côté TX du commutateur – encore une fois, la dénomination est côté hôte. Je ne m’en suis souvenu qu’après avoir fini de router tous les diffpairs, et, après un peu de réflexion, j’ai décidé que c’était ma chance d’essayer les condensateurs 0201. Pour cela, j’ai pris les empreintes de [Christoph]Le merveilleux projet de , intitulé « Effet de la phase de la lune sur le tombstone » – avec un tel nom, ces empreintes doivent être bonnes.

Nous avons déjà parlé des calculs de paires différentielles dans l’un des articles PCIe, et il y avait aussi une vidéo de démonstration ! Cela dit, répétons les calculs sur celui-ci – je montrerai comment passer des « informations sur le site Web de la fabrication de PCB » aux « différences de largeur et de dégagement appropriées », avec quelques raccourcis amusants. Notre configuration consiste, une fois de plus, à avoir des signaux sur les couches externes, référencés à la couche au sol juste en dessous d’eux. Malheureusement, je ne comprends pas encore comment calculer l’impédance différentielle pour les couches de signal prises en sandwich entre deux plans de masse, c’est-à-dire – s’il y a des commentateurs prêts à partager ces connaissances, j’apprécierais énormément votre contribution ! Pour l’instant, je ne vois pas qu’il y aurait un avantage tangible à un tel arrangement, de toute façon.

Un empilement différent pourrait aider

Cette fois, je vais avec un empilement à 4 couches de 0,8 mm – sinon la carte ne rentrera pas dans un socket M.2. Selon les règles de conception, je peux descendre jusqu’à des traces et des espacements de 3,5 mil (0,09 mm), par opposition aux traces habituelles de 6 mil (0,16 mm) auxquelles je suis habitué lorsque je fais des cartes génériques à 2 couches. Au départ, je choisis la variante d’empilage 7628 ici – la principale différence entre les empilements ici est l’épaisseur du préimprégné et la constante diélectrique, ce qui a un impact sur l’épaisseur et l’espacement de diffpair minimum possible.

Cette fois, je vais avec un empilement à 4 couches de 0,8 mm – sinon la carte ne rentrera pas dans un socket M.2. Selon les règles de conception, je peux descendre jusqu’à des traces et des espacements de 3,5 mil (0,09 mm), par opposition aux traces habituelles de 6 mil (0,16 mm) auxquelles je suis habitué lorsque je fais des cartes génériques à 2 couches. Au départ, je choisis la variante d’empilage 7628 ici – la principale différence entre les empilements ici est l’épaisseur du préimprégné et la constante diélectrique, ce qui a un impact sur l’épaisseur et l’espacement de diffpair minimum possible.

Je suis allé par paramètres sur la page d’empilage JLCPCB, et j’ai pris via les paramètres de la page de commande – vous pouvez mettre ces paramètres dans la fenêtre « Fichier => Configuration de la carte », dans l’onglet « Classes réseau ». Après avoir remplacé les paramètres par défaut par ceux du processus contrôlé par impédance à 4 couches – dégagement, largeur de trace minimale, via la taille et autres, – nous obtenons de jolis paramètres que nous pouvons réduire s’il y a un point difficile, et une capacité à faire un placement de composants raisonnablement dense.

Visons aujourd’hui une impédance différentielle ponctuelle de 85 ohms – une excellente cible partout où vous pouvez vous le permettre. Encore une fois, des traces sur le dessus, un plan de masse ininterrompu juste en dessous, sur toute la longueur des paires. Pour l’empilement « 7628 », cela signifie qu’il y a 0,21 mm de matériau avec 4,6 Er entre les paires et le sol – poinçonnez ces deux valeurs dans la calculatrice, laissez l’épaisseur du cuivre à 35 um (1 oz de cuivre), et nous pouvons jouer avec l’espace de trace et les valeurs de largeur, jusqu’à notre limite de 0,09 mm – ce qui nous amène à une option de 0,225 mm de largeur / 0,09 mm d’espace. Ce n’est pas si grand en termes d’espace, cependant.

Visons aujourd’hui une impédance différentielle ponctuelle de 85 ohms – une excellente cible partout où vous pouvez vous le permettre. Encore une fois, des traces sur le dessus, un plan de masse ininterrompu juste en dessous, sur toute la longueur des paires. Pour l’empilement « 7628 », cela signifie qu’il y a 0,21 mm de matériau avec 4,6 Er entre les paires et le sol – poinçonnez ces deux valeurs dans la calculatrice, laissez l’épaisseur du cuivre à 35 um (1 oz de cuivre), et nous pouvons jouer avec l’espace de trace et les valeurs de largeur, jusqu’à notre limite de 0,09 mm – ce qui nous amène à une option de 0,225 mm de largeur / 0,09 mm d’espace. Ce n’est pas si grand en termes d’espace, cependant.

Cependant, vous n’êtes pas obligé de vous en tenir à la pile par défaut ! Après quelques délibérations, je suis passé à l’empilement « 3313 » – avec un préimprégné de 4,05 Er et de 0,1 mm d’épaisseur entre les couches supérieure et intermédiaire. Cela semble être un peu plus cher, mais cela semble un peu plus facile à acheminer dans le peu d’espace dont je dispose. Cela m’a conduit à des paires 0,135 mm / 0,09 mm, tout en gardant la même impédance différentielle de 85 ohms. Maintenant, tout ce que j’ai à faire est d’entrer ces paramètres dans le tableau « Net Classes », et chaque fois que j’appuie sur ‘6’, je commence immédiatement à dessiner une paire différentielle d’impédance de 85 ohms.

Dessin Diffpair

Le CI est placé, les paramètres diffpair sont réglés – nous pouvons commencer à dessiner. N’oubliez pas que l’inversion de la polarité de la paire PCIe n’est pas un crime, c’est une obligation de vous faciliter le routage. D’une manière ou d’une autre, dans cette conception, il n’a pas été nécessaire une seule fois.

Cependant, vous avez besoin d’un peu de patience – l’expérience de dessin de paires différentielles de KiCad n’est pas toujours fluide ; si vous rencontrez des problèmes étranges où une extrémité de la paire ne se connecte pas tout à fait à une autre extrémité, vous n’êtes pas seul. Pour moi, dessiner ces paires était un peu exaspérant. Il est concevable que ce que je traite avec quelque chose communément appelé un problème de compétence – peut-être, il y a un paramètre que je ne remarque pas, car parfois de tels problèmes de « ne pas connecter » sont causés par les contraintes de la RDC. Cependant, dans ce cas, un avertissement s’affichera sur la barre ci-dessus.

Cependant, vous avez besoin d’un peu de patience – l’expérience de dessin de paires différentielles de KiCad n’est pas toujours fluide ; si vous rencontrez des problèmes étranges où une extrémité de la paire ne se connecte pas tout à fait à une autre extrémité, vous n’êtes pas seul. Pour moi, dessiner ces paires était un peu exaspérant. Il est concevable que ce que je traite avec quelque chose communément appelé un problème de compétence – peut-être, il y a un paramètre que je ne remarque pas, car parfois de tels problèmes de « ne pas connecter » sont causés par les contraintes de la RDC. Cependant, dans ce cas, un avertissement s’affichera sur la barre ci-dessus.

N’oubliez pas que chaque fois que votre diffpair traverse la couche supérieure vers la couche inférieure ou vice-versa, il change également les couches de référence, de In1 à In2 respectivement – et vous voudrez ajouter des vias de masse près des vias de diffpair, de sorte que le courant de retour de masse puisse également voyager le long de la paire. Comme d’habitude, quatre vias sont idéaux, trois sont bons, deux sont corrects et un n’est pas idéal mais meilleur que zéro.

Une fois que nous avons dessiné les diffpairs et ajouté les vias de masse, il reste une dernière chose à régler. Alors que les paires PCIe ne doivent pas toutes avoir la même longueur, les deux traces qui composent chaque paire doivent être de la même bout à bout. Pour cela, vous pouvez utiliser l’outil de correction d’inclinaison de paire différentielle – mappé sur 9 sur le clavier. Cela ajoutera une agitation à la piste la plus longue, à l’endroit où une agitation conviendrait le mieux.

Toutes les couches

Lorsque vous dessinez des planches, vous pouvez souvent utiliser une couche interne GND et une couche interne VCC – comme techniquement, VCC et GND peuvent être utilisés comme plans de référence pour les signaux à grande vitesse. Cependant, puisque nous croisons des diffpairs entre les couches supérieure et inférieure, elles auraient alors des références différentes, et c’est encore un territoire inexploré pour moi – je ne sais pas s’il y aurait des problèmes de courant de retour. J’ai commencé avec un plan interne de 1,2 V et un plan interne GND, mais ensuite, alors que je vérifiais mes cartes et écrivais cet article, j’ai parlé avec d’autres ingénieurs, relu un fil de commentaires intéressant sous le premier article de diffpair PCIe, et j’ai décidé de passer aux deux plans internes comme GND.

En ce qui concerne les couches externes où vont les diffpairs, vous voudrez supprimer le remplissage au sol ou l’éloigner, de sorte que le remplissage au sol autour de la paire affectera l’impédance du diffpair – vous verrez très probablement une mise à la terre si vous jetez un œil à n’importe quelle carte PCIe que vous possédez. Ici, je vais acheminer les diffpairs sur les couches externes, mais je ne vais pas supprimer complètement le sol sur celles-ci, en utilisant à la place des exclusions. Tout d’abord, avoir la terre est cool – c’est du cuivre supplémentaire qui peut aider à dissiper la chaleur de l’interrupteur, ou du régulateur de commutation, ou des deux. La deuxième chose est que JLCPCB a récemment été bizarre à propos des remplissages de sol sur des planches denses, et je veux éviter cela.

Jusqu’où l’exclusion doit-elle aller, alors ? La règle 5L (à cinq largeurs de trace) est bonne, ou vous pouvez simplement exclure toute la zone où vous tirez les paires différentielles. Pour nous, 5L signifie 5 * 0,135 mm, soit 0,685 mm de distance entre la paire/via et le remblai. La règle 5L n’est pas une limite stricte – respectez-la autant que possible, mais ne vous inquiétez pas d’avoir quelques vias ici et là. N’oubliez pas que lors du câblage du PCIe, il est important que la chaîne soit humide.

Pour les fils électriques, utilisez vos traces les plus épaisses possibles partout où vous avez de la place. Bien sûr, vous n’avez pas besoin de tirer une piste de 2 mm là où vous voulez mettre 3,3 V, mais avoir des pistes de 0,6 mm ou 1 mm sur un chemin de 3,3 V 1 A est assez ordinaire – certains diront que c’est exagéré, mais si vous avez assez d’espace, il n’y a guère d’avantage à ne pas le faire. Si vous vous demandez ce que vous pouvez faire, il existe des calculateurs de largeur de trace qui vous donneront des valeurs d’augmentation de température et d’inductance, mais la plupart du temps, rendre la trace plus épaisse est une évidence.

Pour les fils électriques, utilisez vos traces les plus épaisses possibles partout où vous avez de la place. Bien sûr, vous n’avez pas besoin de tirer une piste de 2 mm là où vous voulez mettre 3,3 V, mais avoir des pistes de 0,6 mm ou 1 mm sur un chemin de 3,3 V 1 A est assez ordinaire – certains diront que c’est exagéré, mais si vous avez assez d’espace, il n’y a guère d’avantage à ne pas le faire. Si vous vous demandez ce que vous pouvez faire, il existe des calculateurs de largeur de trace qui vous donneront des valeurs d’augmentation de température et d’inductance, mais la plupart du temps, rendre la trace plus épaisse est une évidence.

Après avoir câblé le PCIe et les signaux d’alimentation, il reste quelques éléments. Il peut être tentant de les acheminer sur les couches de sol intérieures – faites de votre mieux pour résister à la tentation, car il existe généralement un meilleur moyen ; avoir des plans intérieurs ininterrompus est largement accepté comme étant un bon mojo pour les diffpairs et pour les signaux en général. Au lieu de cela, considérez d’autres options non standard qui sont moins un péché – par exemple, il est acceptable de retirer les pastilles de soudure d’une empreinte si la pastille n’est pas utilisée, et c’est ce que je vais faire pour tirer l’un des signaux PREST à travers la couche supérieure.

Erreurs et problèmes

À bien des égards, cette conception frappe dans le mille. Il est compact, il s’adapte à tout ce qu’il doit contenir avec de l’espace à revendre, et la puissance à bord est plus que raisonnable. Bien sûr, il y a quelques contretemps possibles que je peux prévoir et que je vérifierai une fois que ces planches seront fabriquées.

À bien des égards, cette conception frappe dans le mille. Il est compact, il s’adapte à tout ce qu’il doit contenir avec de l’espace à revendre, et la puissance à bord est plus que raisonnable. Bien sûr, il y a quelques contretemps possibles que je peux prévoir et que je vérifierai une fois que ces planches seront fabriquées.

Un commutateur PCIe fonctionne à des vitesses élevées, il est donc logique que la consommation d’énergie puisse être un peu sévère, et il en va de même pour la dissipation thermique – en effet, vous verrez des puces à plus grand nombre de ports comme celles-ci recouvertes de dissipateurs thermiques collés sur les adaptateurs chinois ; Ma principale préoccupation est la consommation d’énergie – une carte M.2 E-key devrait consommer au maximum 2 A, et la consommation électrique maximale du commutateur, ainsi que la carte insérée elle-même, pourraient certainement dépasser ce budget.

Pour résoudre ce problème, j’ajoute une entrée d’alimentation séparée et dessine des traces de manière à ce que, si nécessaire, il soit facile de séparer l’entrée 3,3 V du régulateur 1,2 V de l’alimentation de la carte E-key. Ma deuxième préoccupation concernant la consommation d’énergie, cependant, est la dissipation thermique – il n’y a pas beaucoup de masse thermique dans ce PCB, et le chemin de terre n’est pas trop simple, donc la puce pourrait théoriquement surchauffer sous charge. Il n’y aurait pas vraiment de place pour un dissipateur thermique une fois que l’adaptateur est branché sur un ordinateur portable non plus – nous verrons à quel point c’est un problème dans la pratique.

Pour résoudre ce problème, j’ajoute une entrée d’alimentation séparée et dessine des traces de manière à ce que, si nécessaire, il soit facile de séparer l’entrée 3,3 V du régulateur 1,2 V de l’alimentation de la carte E-key. Ma deuxième préoccupation concernant la consommation d’énergie, cependant, est la dissipation thermique – il n’y a pas beaucoup de masse thermique dans ce PCB, et le chemin de terre n’est pas trop simple, donc la puce pourrait théoriquement surchauffer sous charge. Il n’y aurait pas vraiment de place pour un dissipateur thermique une fois que l’adaptateur est branché sur un ordinateur portable non plus – nous verrons à quel point c’est un problème dans la pratique.

Chaque planche peut être une petite expérience, et celle-ci a certainement quelques choses que je n’ai jamais essayées auparavant. J’ai ajouté cette carte à ma dernière commande de PCB, et une fois qu’elle sera arrivée, je partagerai le résultat final avec vous tous, d’une manière ou d’une autre. Jusque-là, les fichiers sont sur GitHub, et j’espère que l’histoire de cette carte vous donnera beaucoup d’informations sur la conception avec PCIe !